Design and Implement of High-speed Receiving Cache System of the Satellite

-

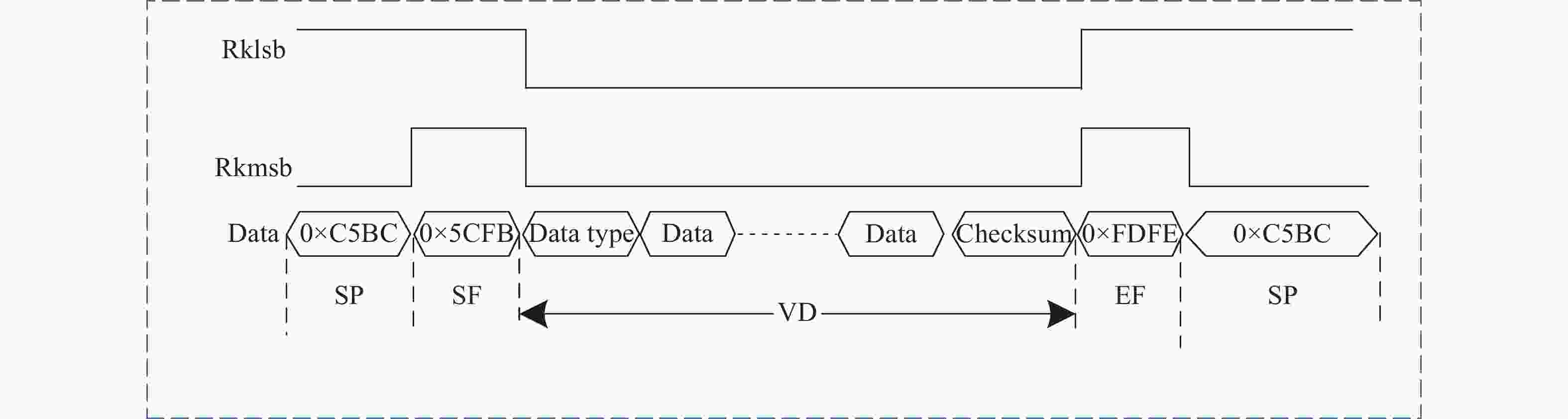

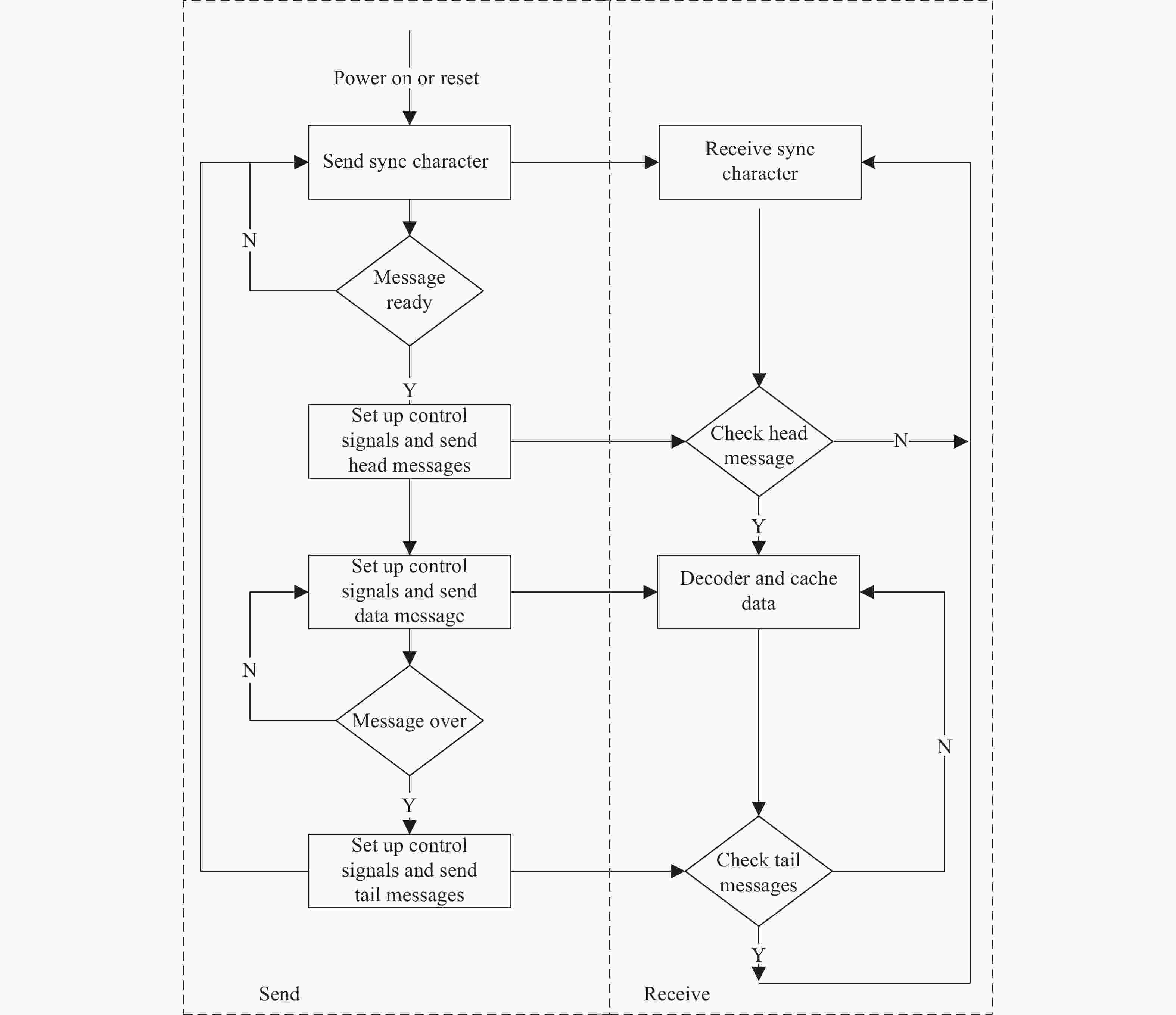

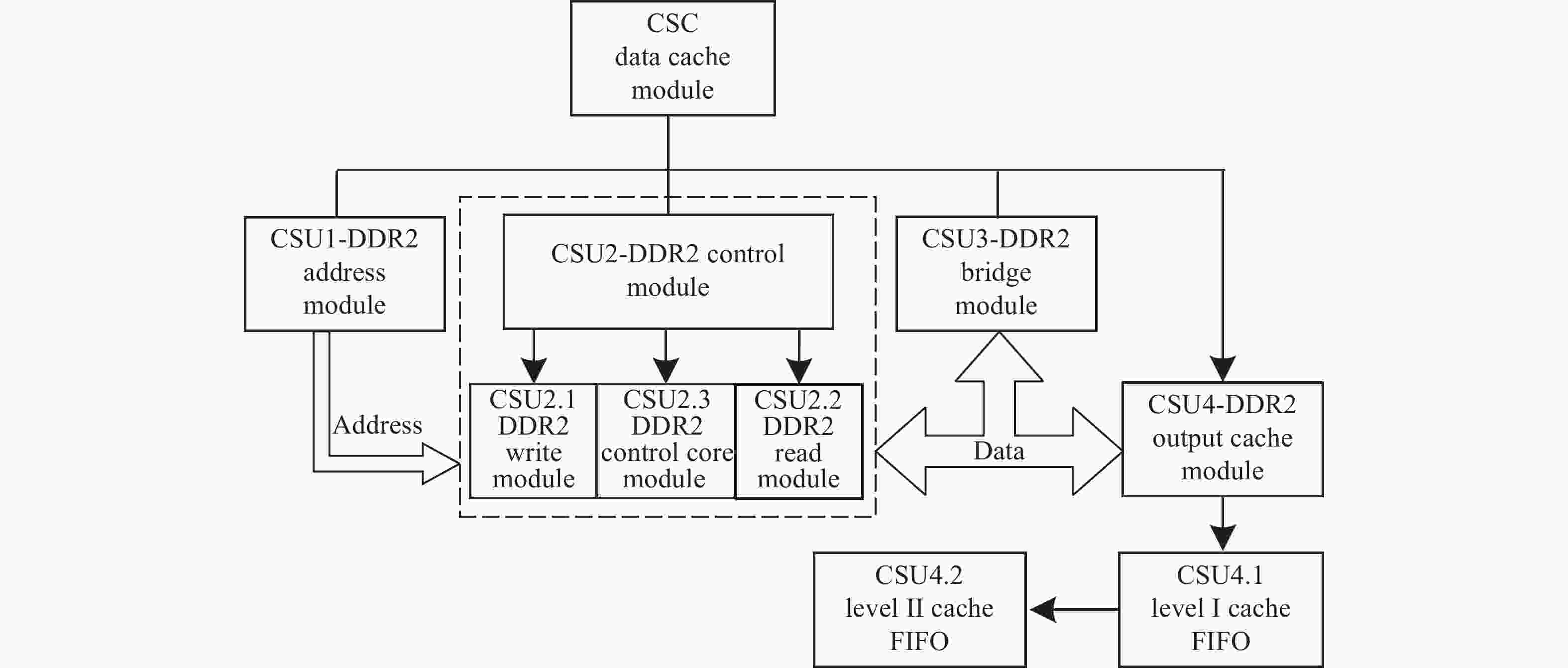

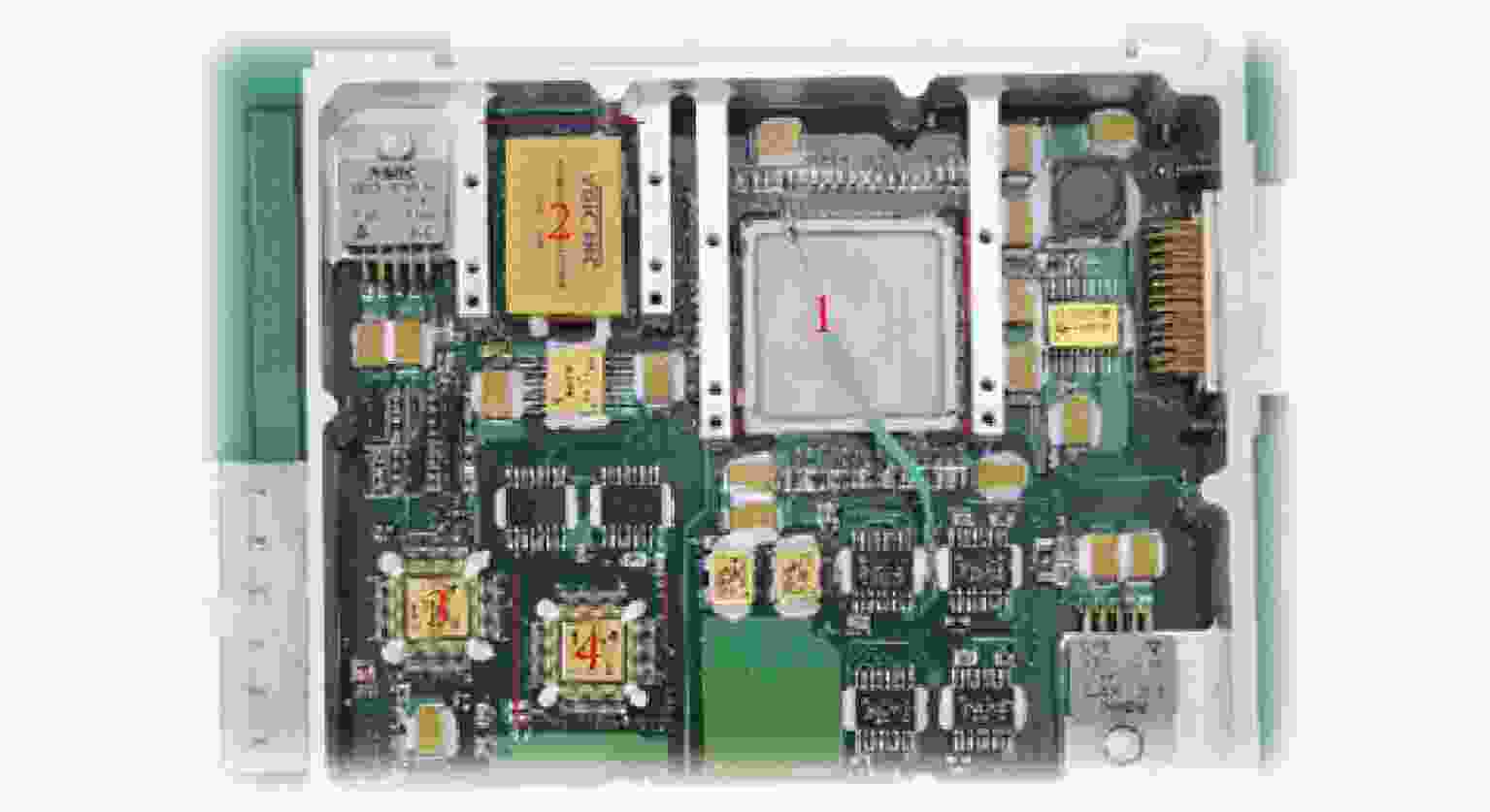

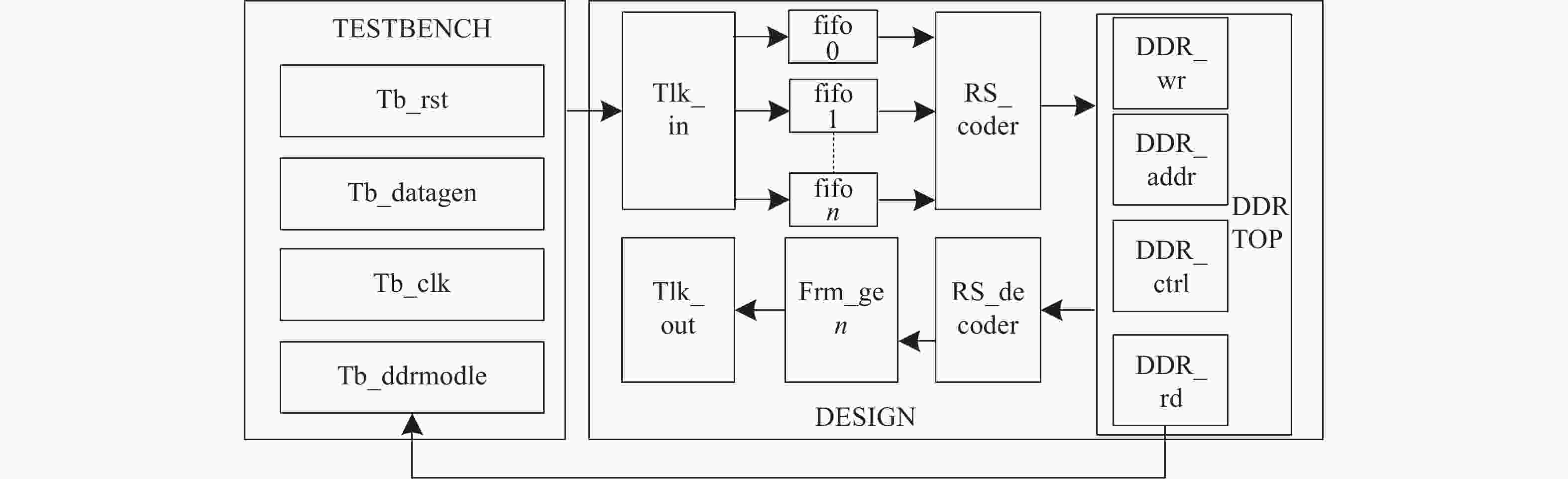

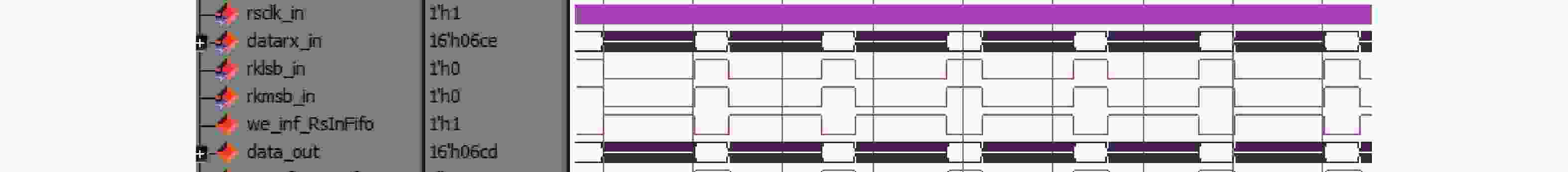

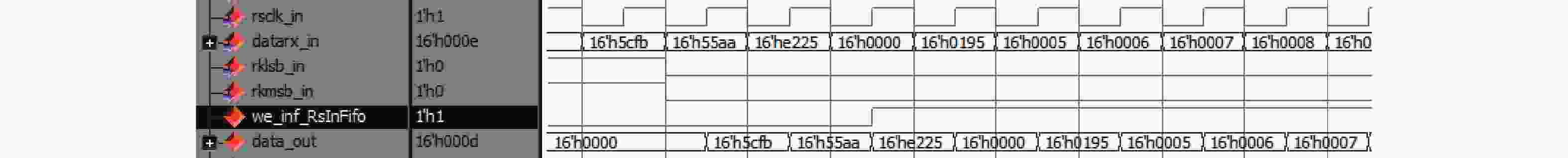

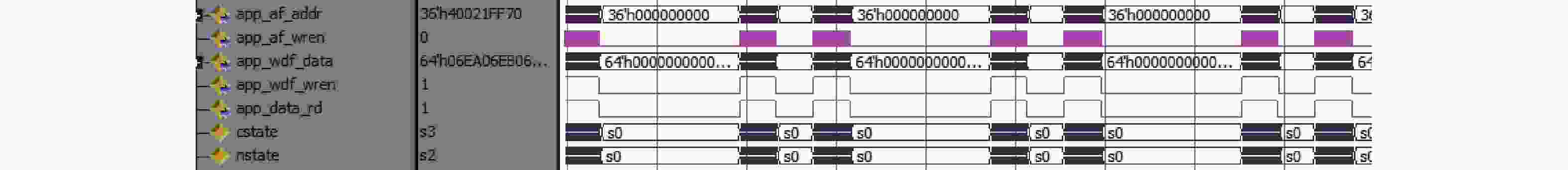

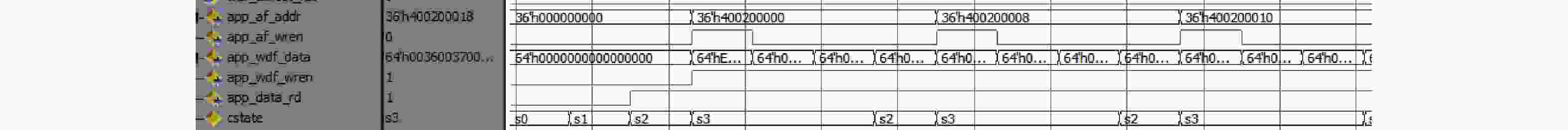

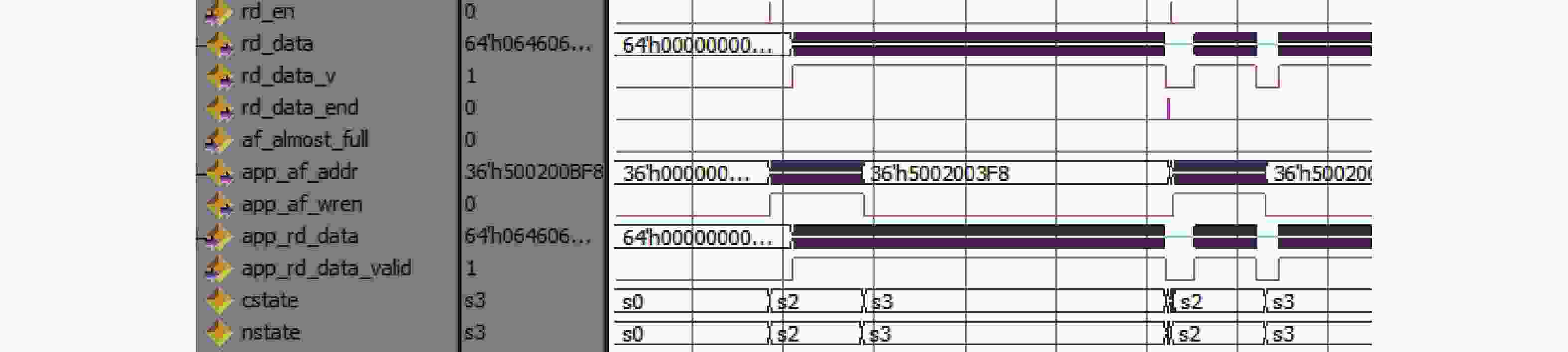

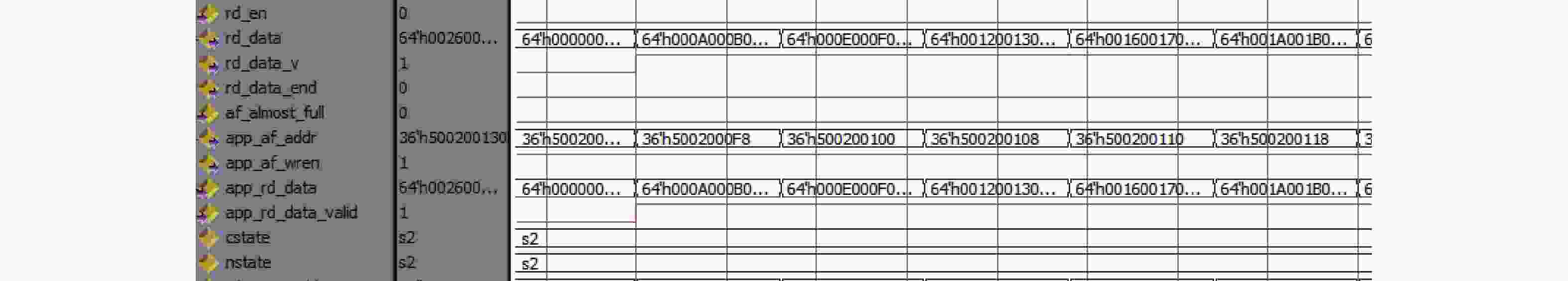

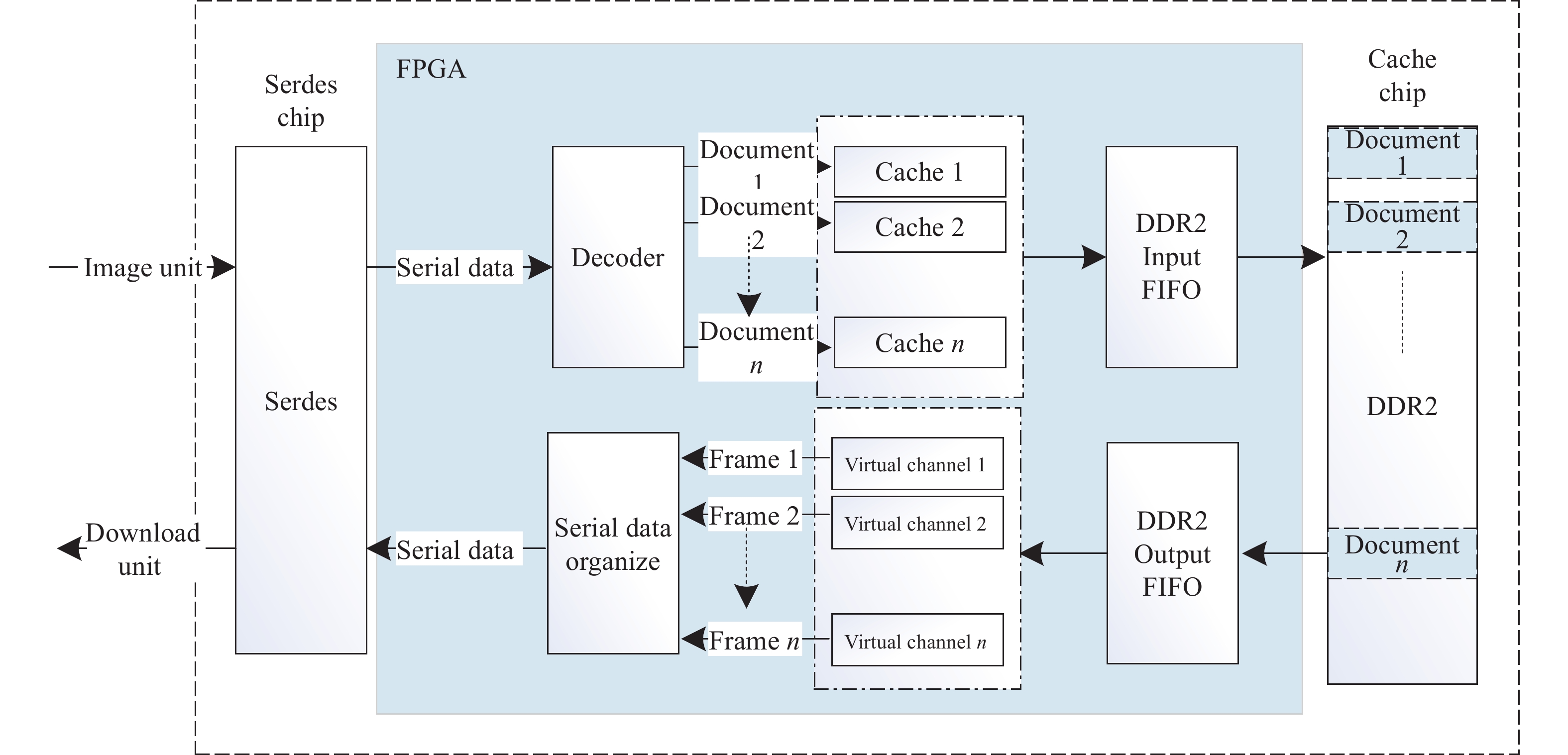

摘要: 遥感卫星图像数据量的高速增长,以及遥感卫星搭载的相机不同工作模式下产生的数据差异化处理的需求,为星间数据处理带来了巨大挑战。针对星载Gbit·s–1级高速数据收发及文件缓存等星间数据处理面临的问题,以百兆每秒级星载高速接收缓存系统为切入点,以遥感卫星数据处理的发展为依据,在分析SerDes传输原理的基础上,采用模型仿真和工程验证的方法,制定了高速串行数据链路层传输协议SSLLP(Satellite Serial Link Layer Protocol)和类文件化高速缓存的策略。在硬件设计和软件开发的基础上,最终完成了具备处理入口速率3.2 Gbit·s–1并能以类文件化的方式缓存64个数据文件的星载数据处理单元的工程实现。测试结果表明,基于SSLLP的高速串行数据接收正确,缓存策略有效,系统高效可靠。该设计已在某型号任务中取得在轨验证,为星载高速串行数据处理系统提供了参考。Abstract: Recently with the development of space technology, the explosive growth of remote sensing satellite image data and the demand for multi-mode operation of a remote sensing satellite camera, have produced the differential processing of different data. At the same time, it also has brought great challenges for inter-satellite data processing. The purpose of this research is to solve the problems of inter-satellite data processing, such as gigabits per second high-speed data transceiver, datas storage, file cache and so on. This study investigates the development of remote sensing satellite data processing, analyzes the transmission principle of SerDes, and formulates the operation strategy of documented class of high-speed cache. Based on hardware design and software development, the project of high-speed space-borne data processing unit with 3.2 bit·s–1 level and 64 data documents is completed. The test results show that based on SSLLP (Satellite Serial Link Layer Protocol), the high-speed serial data reception is correct and the cache strategy is effective. Most important of all, the system is efficient and reliable. This design has been applied to some on-orbit model missions, providing a reference to the design of high-speed receiving cache system of the satellite.

-

Key words:

- Space-borne /

- High speed serial bus /

- Data processing

-

表 1 眼图信息对比

Table 1. Eye diagram information comparison

Parameter Eye width/

psEye height/

mVEye zero/

mVEye one/

mVEye jit/

psData rate/

(bit·s–1)Q-factor Crossing/

(%)DutCyc

dist/(%)Eye Display 1 435.6 970 771.4 756.9 151.3 1.60 12.2 48.6 7 Eye Display 2 452.8 1072 807.7 809 131.7 1.60 12.44 48.8 6.8 -

[1] 方忆平, 柏芸. 通信导航遥感卫星应用实践与思考[J]. 国防科技工业, 2021(3): 52-55FANG Yiping, BO Yun. Application practice and thinking of communication navigation remote sensing satellite[J]. Defence Science & Technology Industry, 2021(3): 52-55 [2] 梁晓珩, 梁秀娟, 柯蓓. 我国遥感卫星系统发展进阶路径探讨[J]. 航天器环境工程, 2021, 38(1): 100-105 doi: 10.12126/see.2021.01.016LIANG Xiaoheng, LIANG Xiujuan, KE Bei. The development path of romote sensing satellite system in China[J]. Spacecraft Environment Engineering, 2021, 38(1): 100-105 doi: 10.12126/see.2021.01.016 [3] 张庆君. 高分三号卫星总体设计与关键技术[J]. 测绘学报, 2017, 46(3): 269-277 doi: 10.11947/j.AGCS.2017.20170049ZHANG Qingjun. System design and key technologies of the GF-3 satellite[J]. Acta Geodaetica et Cartographica Sinica, 2017, 46(3): 269-277 doi: 10.11947/j.AGCS.2017.20170049 [4] 王连国, 朱岩, 沈卫华, 等. 暗物质粒子探测卫星的集中式载荷管理系统[J]. 空间科学学报, 2018, 38(4): 567-574 doi: 10.11728/cjss2018.04.567WANG Lianguo, ZHU Yan, SHEN Weihua, et al. Centralized payload management system for dark matter particle explorer satellite[J]. Chinese Journal of Space Science, 2018, 38(4): 567-574 doi: 10.11728/cjss2018.04.567 [5] 孙允珠, 蒋光伟, 李云端, 等. 高分五号卫星方案设计与技术特点[J]. 上海航天, 2019, 36(S2): 1-13 doi: 10.19328/j.cnki.1006-1630.2019.S.001SUN Yunzhu, JIANG Guangwei, LI Yundun, et al. GF-5 satellite system design and technological characteristics[J]. Aerospace Shanghai, 2019, 36(S2): 1-13 doi: 10.19328/j.cnki.1006-1630.2019.S.001 [6] 刘辉, 姜通, 郭强, 等. 高分五号卫星高效高速数据传输技术研究[J]. 上海航天, 2019, 36(S2): 30-36 doi: 10.19328/j.cnki.1006-1630.2019.S.005LIU Hui, JIANG Tong, GUO Qiang, et al. Research on efficient high-speed data transmission technology for GF-5 satellite[J]. Aerospace Shanghai, 2019, 36(S2): 30-36 doi: 10.19328/j.cnki.1006-1630.2019.S.005 [7] 郑小松, 李立, 张雨, 等. 高分七号卫星数据处理与传输分系统设计与验证[J]. 航天器工程, 2020, 29(3): 74-81 doi: 10.3969/j.issn.1673-8748.2020.03.012ZHENG Xiaosong, LI Li, ZHANG Yu, et al. Design and verification of data processing and transmission subsystem on GF-7 satellite[J]. Spacecraft Engineering, 2020, 29(3): 74-81 doi: 10.3969/j.issn.1673-8748.2020.03.012 [8] 庾志衡, 叶俊明, 邓迪文. 基于FPGA与DDR2 SDRAM的大容量异步FIFO缓存设计[J]. 微型机与应用, 2011, 30(4): 34-36,40YU Zhiheng, YE Junming, DENG Diwen. A design of high speed and deep asynchronous FIFO based on FPGA and DDR2 SDRAM[J]. Microcomputer & Its Applications, 2011, 30(4): 34-36,40 [9] 韩笑, 闫永立, 李勇彬, 等. 基于FPGA的DDR2_SDRAM控制器用户接口设计[J]. 电子设计工程, 2021, 29(1): 168-171,176 doi: 10.14022/j.issn1674-6236.2021.01.035HAN Xiao, YAN Yongli, LI Yongbin, et al. The design of DDR2-SDRAM controller user interface based on FPGA[J]. Electronic Design Engineering, 2021, 29(1): 168-171,176 doi: 10.14022/j.issn1674-6236.2021.01.035 [10] 张媚, 杜辉, 关晖, 等. 基于TLK2711的遥感卫星高速串行载荷数据接口设计[J]. 航天器工程, 2015, 24(6): 13-19 doi: 10.3969/j.issn.1673-8748.2015.06.003ZHANG Mei, DU Hui, GUAN Hui, et al. Design of satellite high-speed serial data interface based on TLK2711[J]. Spacecraft Engineering, 2015, 24(6): 13-19 doi: 10.3969/j.issn.1673-8748.2015.06.003 [11] 吕文强, 施睿, 任勇峰, 等. 基于DDR2 SDRAM的高速数据缓存技术研究[J]. 电子测量技术, 2020, 43(18): 6-10LÜ Wenqiang, SHI Rui, REN Yongfeng, et al. Research on high speed data cache technology based on DDR2 SDRAM[J]. Electronic Measurement Technology, 2020, 43(18): 6-10 [12] Texas Instruments Incorporated. Tlk2711-SP 1.6-Gbps To 2.5-Gbps Class V Transceiver[Z]. Texas: Texas Instruments Incorporated, 2012 [13] 沈竞宇. 基于SerDes芯片8 b/10 b编解码电路的设计及验证[D]. 成都: 电子科技大学, 2011SHEN Jingyu. Design and Verification of 8 b/10 b Code Circuit Based on SerDes Chip[D]. Chengdu: University of Electronic Science and Technology of China, 2011 [14] 余达, 刘金国, 徐东, 等. 多路基于TLK2711高速串行图像数据的传输系统[J]. 液晶与显示, 2017, 32(10): 815-821 doi: 10.3788/YJYXS20173210.0815YU Da, LIU Jinguo, XU Dong, et al. Design of multi channel high-speed serial image data transmission system based on TLK2711[J]. Chinese Journal of Liquid Crystals and Displays, 2017, 32(10): 815-821 doi: 10.3788/YJYXS20173210.0815 [15] 杜旭, 于洋, 黄建. 基于FPGA的高速串行传输接口的设计与实现[J]. 计算机工程与应用, 2007, 43(12): 94-96 doi: 10.3321/j.issn:1002-8331.2007.12.032DU Xu, YU Yang, HUANG Jian. Design and implementation of high-speed serial transmission interface based on FPGA[J]. Computer Engineering and Applications, 2007, 43(12): 94-96 doi: 10.3321/j.issn:1002-8331.2007.12.032 -

-

下载:

下载: